© 1981 IEEE. Personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works must be obtained from the IEEE.

# IEEE Transactions on Nuclear Science, Vol. NS-28, No. 3, June 1981

## DESIGN OF CMOS/SOS CIRCUITS FOR SPACE APPLICATIONS

### Ludek Kitajewski\*

## I. Abstract

Requirements of integrated circuits for space applications are high speed, small size and great reliability. The CMOS/SOS process technology inherently fulfills these requirements.

Recently discovered problems of reliability are soft errors or "bit-flips" induced by galactic cosmic rays or terrestrial  $\propto$ -particles.

This paper discusses CMOS/SOS circuit design which minimizes these errors. A design example is given for D flip-flop as a typical storage element, and a comparison is made between 4  $\mu$ m, 2  $\mu$ m, and 1  $\mu$ m channel lengths.

Results obtained for short channel lengths indicate that the design of VLSI circuits for space applications with CMOS/SOS technology is feasible and realistic.

### II. Introduction

Errors caused by galactic cosmic rays and  $\propto$ particles radiating from package materials have been reported by many investigators. (1) - (8)

The purpose of this work is to show that by using CMOS/SOS silicon gate technology and by a judicious choice of process and circuit design parameters these error rates can be made very small even for the contemporary and future technologies of very short channel lengths down to  $1 \ \mu m$ .

While purer packaging materials can considerably alleviate the  $\alpha$ -particle problems, shielding of ICs cannot entirely eliminate cosmic ray induced errors due to the varied nature and high energy spectra of the cosmic rays. (9) Thus careful design of the circuits based on the understanding of the mechanism of error generation is needed. In previous publications models of mechanisms of soft-error generation were proposed for bipolar J-K flip-flop(1) and NMOS dynamic RAM. (10) These models were extended to static CMOS RAMS and PMOS shift registers. (11)

Similarly using an appropriate model for the CMOS/ SOS silicon gate technology the cosmic ray induced error rates can be calculated. Calculations involve determination of the minimum deposited energy in the sensitive volume,  $E_{min}$ , and of the stopping power, dE/dx, for the critical node of the circuit analyzed. Error rates are then found from the value of the cosmic ray flux of particles which are capable of causing errors. These calculations follow a previously described method. (10) A summary of the method of calculations of error rates is given below:

$$E_{\min} = 22.5 \times Q_c \times f (MeV)$$

(1)

where,

Q<sub>c</sub> = critical charge on the sensitive node (picocculombs) and,

f

= ionization collection efficiency usually

assumed 100 percent, hence, f = 1

$$Q_{c} = C_{T} \times \Delta V$$

(2)

where,

$$C_{T} = C_{g} + C_{m} + C_{j} + C_{ov}$$

(3)

$$\Delta V \approx 0.8 \times V_{\rm DD} \tag{4}$$

C<sub>T</sub> = total storage node capacitance

- C<sub>g</sub> = gate capacitance

- C<sub>m</sub> = metal interconnect capacitance

- $C_i = p-n$  junction capacitance

- C<sub>ov</sub> = gate over drain and source overlap capacitance (equals zero for selfaligned gate technology)

where,

- w = gate width

- t = silicon layer width

- $h_d$  = depletion junction width

$$\overline{A}_{p}$$

= average projected area (6)

= 1/2 (w x t + w x h\_d + t x h\_d)

$$\overline{S}$$

= average path length =  $V_S / \overline{A}_p$  (7)

$$\frac{dE}{dx} = \frac{E_{\min}}{\overline{S} \times d_{si}}$$

(8)

where,

$d_{si}$  = density of Si = 2.4 gm/cm<sup>3</sup>

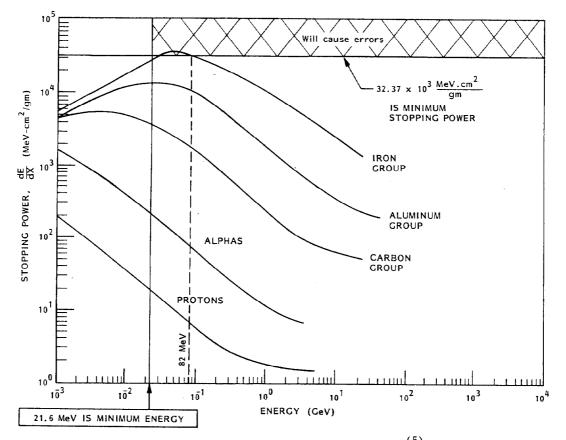

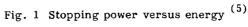

Using the calculated value of  $E_{min}$  and dE/dx the energy ranges of particles capable of causing errors can be found for various groups of particles from Fig. 1. Then, the total flux of particles that can cause errors can be found from Fig. 2 for each group of particles. The sum of these fluxes multiplied by the average projected area gives the error rate, or

$$E_{R} = error rate = {}^{\phi}E_{T} \times \overline{A}_{p} \times 0.5 \qquad (9)$$

The factor 0.5 is due to the fact that error can occur only when "1" is stored which happens 1/2 of the time.

Manuscript received December 23, 1980.

\*Lockheed Microelectronics Center, Sunnyvale, California 94086

0018-9499/81/0600-3569\$00.75©1981 IEEE

Fig. 2 Estimated differential omnidirectional flux, galactic cosmic rays, z > 2 <sup>(5)</sup>

3570

;

۰,-

### III. Design Considerations

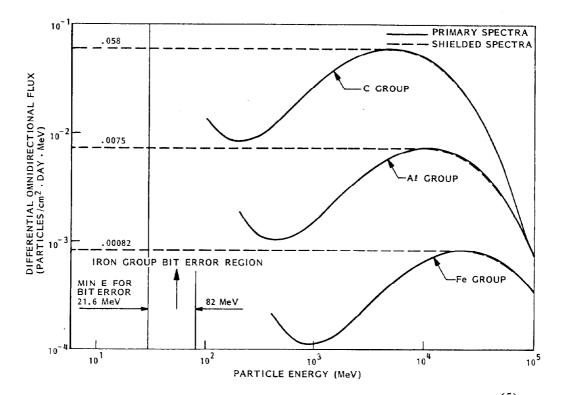

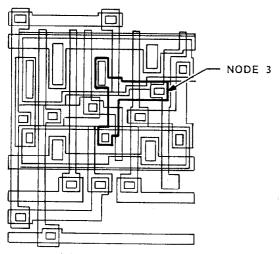

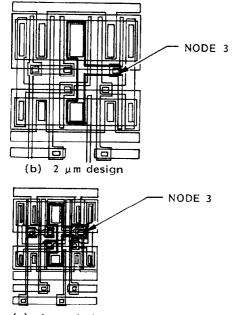

In order to investigate the speed, power consumption, size, reliability and yield of CMOS/SOS process technology three identical circuits were designed with various design rules, namely 4  $\mu$ m, 2  $\mu$ m, and 1  $\mu$ m. These circuits consisted of a 16-bit shift register, input and output buffers, and an input protection network. The basic 1-bit circuit was a D-type flip-flop and is shown in Fig. 3.

Design of the D-type flip-flop was optimized for the lowest cosmic ray induced error rate without jeopardizing the circuit speed and size. The following design criteria were used:

#### Storage Capacitance

For a low error rate, high critical charge and hence large storage capacitance are required. In self-aligned gate technology  $C_{\rm OV}$  is zero. Metal interconnect capacitance contributes very little to the total capacitance. Junction capacitance depends on the doping concentrations which determines the depletion layer width and on the silicon layer thickness. Neither of these parameters can be manipulated significantly to increase total storage capacitance. Hence, only by making  $C_g$  large, could the total storage capacitance be increased. This was done by keeping  $t_{\rm OX}$  small and scaling it down for 2  $\mu$ m and 1  $\mu$ m designs and by keeping w large.

#### Device Dimensions, w and 1

Channel length, 1, is fixed for a particular design, hence w becomes the controlling parameter. Making w large improves the speed and lowers the error rate. The speed is improved because of higher w/l ratio which means lower device "ON" resistance, and the error rate is reduced because with larger w dimension,  $C_g$  and  $C_j$  both increase, and hence the storage charge increases. Dimension w is limited mainly by chip size and power consumption.

#### Power Supply, VDD

From expressions (2) and (4), it can be seen that the higher the  $V_{DD}$  the larger the storage charge and hence the lower the error rate. A  $V_{DD}$ of 10V was chosen for 4  $\mu$ m design and was scaled down to 7.5V and 5.0V for 2  $\mu$ m and 1  $\mu$ m designs, respectively. The supply voltage  $V_{DD}$  is limited by device breakdown voltages, by availability and standardization and by power consumption considerations.

#### Sensitive Volume

Error rate is a function of the sensitive volume. The smaller the sensitive volume, the shorter the average path length and hence the higher the stopping power, see expressions (7) and (8). Now from Fig. 1 it can be seen that higher stopping power reduces the number of cosmic ray particles which can cause error. Thus smaller sensitive volume results in lower error rate provided the storage capacitance is constant. In this design a small sensitive volume was achieved by using SOS process with ion implant for source and drain sufficiently deep to go through the entire silicon island thickness of  $0.5 \ \mu$ m, and by making the n-p junction approximately linearly graded which resulted in lower depletion width. Thus the SOS process has an inherently small sensitive volume.

## Scaling Factor

For very short channel devices scaling of some parameters is necessary (12). This usually involves parameters  $t_{\rm OX}$ , gate oxide thickness,  $V_{\rm DD}$ , power supply voltage and  $N_{\rm A}$ ,  $N_{\rm D}$ , doping concentrations. Customarily a scaling constant, K, is taken as the ratio of the channel length of the standard device to that of the scaled-down device. Thus, scaling down from 4  $\mu$ m design to 1  $\mu$ m design, for example, would make K = 4. Therefore,  $t'_{\rm OX}$ ,  $V_{\rm DD}'$ ,  $N'_{\rm A}$  and  $N'_{\rm D}$  of the 1  $\mu$ m design device should be 1/4  $t_{\rm OX}$ ,  $1/4~V_{\rm DD}$ , 4  $N_{\rm A}$  and 4  $N_{\rm D}$  of the 4  $\mu$ m device. This rule was followed for  $t_{\rm OX}$ ,  $N_{\rm A}$  and  $N_{\rm D}$ , but a reduced scaling factor was taken for  $V_{\rm DD}$  in order to keep  $Q_{\rm c}$  high and the error rate low, see expressions (2) and (4). Thus, the values of  $V_{\rm DD}$  taken for the 4  $\mu$ m, 2  $\mu$ m, and 1  $\mu$ m designs were 10V, 7.5V, and 5.0V, respectively. These supply voltages should not cause any breakdown problems.

### IV. Error Rate Calculations

Cosmic ray induced error rate calculations were carried out for  $4 \mu m$ ,  $2 \mu m$ , and  $1 \mu m$  designs. Node 3 of the D flip-flop was the critical node, see Fig. 3. The method followed is outlined in the introduction.

### Error Rate of the 4 µm Design

Table 1 shows the parameters used for the design.

Using the parameters from Table 1 and the areas from chip layout shown in Fig. 4, we get

| с <sub>g</sub> | = | 0.069 pF  |  |  |

|----------------|---|-----------|--|--|

| cm             | = | 0.0340 pF |  |  |

| ci             | = | 0.0170 pF |  |  |

| Parameter                          | Symbol          | Nominal Value                                                                                                                                                           |  |  |

|------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Gate oxide                         | t <sub>ox</sub> | 1050 Å                                                                                                                                                                  |  |  |

| Silicon island thickness           | t               | $0.5 \ \mu \mathrm{m}$                                                                                                                                                  |  |  |

| Depletion region width             | h <sub>d</sub>  | 1.2 μm                                                                                                                                                                  |  |  |

| Side diffusion                     | h <sub>s</sub>  | 0.1 μm                                                                                                                                                                  |  |  |

| Gate capacitance per unit area     | $C_{g}/A_{g}$   | $0.34 \times 10^{-3} \text{ pF}/\mu \text{m}^2$                                                                                                                         |  |  |

| Metal capacitance per unit area    | $C_m/A_m$       | $0.064 \times 10^{-3} \text{ pF}/\mu \text{m}^2$                                                                                                                        |  |  |

| Junction capacitance per unit area | $C_j/A_j$       | $\begin{array}{c} 0.25 \times 10^{-3}  \text{pF} / \mu \text{m}^2 \text{ for p-type} \\ 0.52 \times 10^{-3}  \text{pF} / \mu \text{m}^2 \text{ for n-type} \end{array}$ |  |  |

| Supply voltage                     | v <sub>DD</sub> | 10V                                                                                                                                                                     |  |  |

Table 1 Electrical and physical parameters of the 4  $\mu\,m$  CMOS/SOS circuits

(a) 4 μm design

(c) 1  $\mu$ m design Fig. 4 Layout of the D-type flip-flop hence,

$$C_{T} = 0.12 \text{ pF}$$

and,

$$Q_{c} = 0.96 \, pC$$

Therefore,

$E_{min} = 21.6 \text{ MeV}$

Using the device dimensions of the critical node, we get

$$V_{s} = 58.8 \ \mu m^{3}$$

$\overline{A}_{p} = 21.1 \ \mu m^{2}$

$\overline{S} = 2.78 \ \mu m$

hence,

$$(dE/dx)_{min} = \frac{32.37 \times 10^3 \text{ MeV} \times \text{cm}^2}{\text{gm}}$$

With this value of the stopping power only the iron group particles contribute to errors. From Fig. 1 the energy range is 21.6 MeV to 82 MeV, and from Fig. 2 the total flux is:

$\phi_{\rm ET} = 0.050 \, {\rm particles/cm^2 \ x \ day}$

Therefore, the error rate per device is:

$$E_{R} = \phi_{ET} \times \overline{A}_{p} \times 0.5 = 0.53 \times 10^{-8} \text{ errors} / \text{ day}$$

# Error Rate of the 2 $\mu$ m and 1 $\mu$ m Design

Similar calculations were carried out for 2  $\mu\,m$  and 1  $\mu\,m$  designs, except that some parameters were scaled down as follows:

2

$$\mu$$

m design, t<sub>ox</sub> = 525 Å

$V_{DD}$  = 7.5V

1  $\mu$ m design, t<sub>ox</sub> = 262 Å

$V_{DD}$  = 5V

Due to scaling, some parameters shown in the Table 1 above were modified as follows:

$C_g/A_g = 0.68 \times 10^{-3} \text{ pF}/\mu\text{m}^2 \text{ for } 2 \ \mu\text{m} \text{ design}$   $1.35 \times 10^{-3} \text{ pF}/\mu\text{m}^2 \text{ for } 1 \ \mu\text{m} \text{ design}$   $C_j/A_j = 0.285 \times 10^{-3} \text{ for } 2 \ \mu\text{m} \text{ and } \text{p-channel}$   $0.594 \times 10^{-3} \text{ for } 2 \ \mu\text{m} \text{ and } \text{n-channel}$   $0.344 \times 10^{-3} \text{ for } 1 \ \mu\text{m} \text{ and } \text{p-channel}$  $0.715 \times 10^{-3} \text{ for } 1 \ \mu\text{m} \text{ and } \text{n-channel}$

For  $C_j/A_j$  calculations a square law relationship of junction capacitance and reverse bias was assumed. The formula used was:

$$C_{j}/A_{j} = \frac{C_{j}o}{\left(1 + \frac{V_{R}}{|\phi_{\beta}|}\right)^{1/2}}$$

(6)

where,

$C_{j0}$  = junction capacitance at zero bias  $V_R$  = reverse bias across the junction and

$$|\phi_{\beta}|$$

= absolute value of the bulk junction

potential (0.6V was taken at 25°C)

The summary of results is shown in Table 2.

# V. Discussion of Results

Considering the design goal of very high speed of operation (above 100 MHz for 4  $\mu$ m design), the CMOS/SOS circuits for technology and reliability evaluations show a very low error rate. This was achieved by maximizing storage charge and minimizing sensitive volume, without significantly lowering the operating speed. Storage charge was made large by choosing comparatively high power supply voltage and high w/l ratio, which resulted in higher gate and junction capacitances and, at the same time, higher speed of operation. The sensitive volume was made small by using an all ion implant process for depletion through the silicon layer which reduced the depletion region and produced short side diffusion (only due to annealing a approximately 850°C).

Since in the SOS technology source and drain diffusions extend all the way through the silicon layer to the sapphire interface, the depletion region

| Parameter                            |                  | Dimension                                         | C                      | MOS/SOS D Flip-F        | lop                          |

|--------------------------------------|------------------|---------------------------------------------------|------------------------|-------------------------|------------------------------|

|                                      | Symbol           |                                                   | 4 μm Design<br>Rules   | 2 μm Design<br>Rules    | 1 μm Design<br>Rules         |

| Gate capacitance                     | Cg               | pF                                                | 0.069                  | 0.052                   | 0.037                        |

| Metal capacitance                    | C <sub>m</sub>   | pF                                                | 0.034                  | 0.027                   | 0.015                        |

| Junction capacitance                 | с <sub>ј</sub>   | pF                                                | 0.017                  | 0.015                   | 0.013                        |

| Total storage capacitance            | C <sub>T</sub>   | pF                                                | 0.120                  | 0.094                   | 0.065                        |

| Supply voltage                       | v <sub>DD</sub>  | V                                                 | 10.0                   | 7.5                     | 5.0                          |

| Critical charge                      | Qc               | pC                                                | 0.960                  | 0.564                   | 0.260                        |

| Minimum deposited energy             | E <sub>min</sub> | MeV                                               | 21.6                   | 12.7                    | 5.9                          |

| Sensitive volume                     | v <sub>s</sub>   | μm <sup>3</sup>                                   | 58.8                   | 45.6                    | 32.4                         |

| Average projected area               | Āp               | $\mu$ m <sup>2</sup>                              | 21.1                   | 16.5                    | 11.8                         |

| Average path length                  | Īp               | μm                                                | 2.78                   | 2.76                    | 2.75                         |

| Stopping power                       | $\frac{dE}{dx}$  | $\frac{\text{MeV} \times \text{cm}^2}{\text{gm}}$ | $32.37 \times 10^3$    | $19.17 \times 10^3$     | $8.94 \times 10^3$           |

| Energy range                         | ΔΕ               | MeV                                               | C:0<br>A1:0<br>Fe:60.4 | C:0<br>A1:0<br>Fe:407.3 | C:0<br>A1:142.5<br>Fe:1792.5 |

| Total error-causing<br>particle flux | ¢ET              | Particles<br>cm <sup>2</sup> x day                | 0.050                  | 0.334                   | 2.54                         |

| Error rate for a single S.R. bit     | <sup>E</sup> R   | errors<br>day                                     | $0.53 \times 10^{-8}$  | $2.7 \times 10^{-8}$    | $15.0 \times 10^{-8}$        |

| Table 2 | Error | rate | calculations |  | summary | of | results |

|---------|-------|------|--------------|--|---------|----|---------|

|---------|-------|------|--------------|--|---------|----|---------|

of the p-n junctions and hence the sensitive volume are greatly reduced. This reduction, however, results in lower  $C_j$  and hence in lower  $E_{min}$ , which causes a higher error rate.

The best approach for high speed and good immunity from cosmic ray radiation is to design for a high w/l ratio, thin gate oxide and high supply voltage and to use CMOS/SOS technology with all ion implant deep diffusion process and linearly graded p-n junctions.

## VI. Conclusions

Circuits for the evaluation of the speed of operation, power consumption, size, reliability and yield were designed using CMOS/SOS technology. The design was optimized for a low error rate of cosmic ray induced errors. Error rates for three different designs were calculated. These designs had identical circuit schematics, but different design rules and were characterized by channel lengths of 4  $\mu$ m, 2  $\mu$ m, and 1  $\mu$ m. Low error rates obtained for these circuits indicate that the VLSI circuits suitable for space applications can be fabricated with optimized design parameters fully compatible with the contemporary short channel length CMOS/SOS technology.

# VII. Acknowledgment

The author wishes to thank Dr. J. C. Lee for many useful suggestions and the help given in calculations of the error rates and to Drs. K. Greenough and D. H. Phillips for reviewing the paper and supporting this work.

#### References

- Binder, D., Smith, E. C., and Holman, A. B., "Satellite Anomalies from Galactic Cosmic Rays," IEEE Trans. on Nuclear Science. Vol. NS-22, No. 6, December 1975, pp. 2675-2680.

- Phillips, D. H., "Cosmic Radiation Effects in Spacecraft Microelectronics," Part I, Military Electronics/Countermeasures, August 1979, pp. 88-92.

Ludek Kitajewski has responsibility for silicon-on-sapphire and MOS integrated circuit design as a member of the technical staff within the Lockheed Microelectronics Center. He received his B. Sc (Eng.) degree in Electronics from London University in 1955 and completed courses in Semiconductor Physics and Transistor Physics and Transistor Circuit Design at the graduate school of Northeastern

University in Boston. Mr. Kitajewski has been involved in semiconductor work and integrated circuit design since 1963. Prior to joining the Lockheed Microelectronics Center in 1978, he has engaged in the design of LSI MOS circuits including calculators, microprocessors and non-volatile memories.

- Phillips, D. H., "Cosmic Radiation Effects in Spacecraft Microelectronics." Part II, Military Electronics/Countermeasures, September 1979, pp. 87-93.

- Kolasinski, W. A., Blake, J. B., Anthony, J. K., Price, W. E. and Smith, E. C., "Simulation of Cosmic Ray Induced Soft Errors and Latchup in Integrated-Circuit Computer Memories," IEEE Trans. on Nuclear Science, Vol. NS-26, No. 6, December 1979.

- Brucker, G. J., Chater, W. and Kolasinski, W. A., "Simulation of Cosmic Ray Induced Errors in CMOS/SOS Memories," IEEE Trans. on Nuclear Science, Vol. NS-27, No. 6, December 1980

- May, T. C. and Woods, M. H., International Reliability Physics Symposium, San Diego, Calif., April 1978.

- Redman, D. J., Sega, R. M. and Joseph, R., "Alpha Particle-Induced Soft Errors in Microelectronic Devices," Part I, Military Electronics/ Countermeasures, March, 1980, pp. 42-47.

- Redman, D. J., Sega, R. M. and Joseph, R., "Alpha Particle-Induced Soft Errors," Part II, Military Electronics/Countermeasures, April, 1980, pp. 40-48.

- Phillips, D. H. and Lee, J. C., "Cosmic Ray Properties and the Effect of Cosmic Radiation on Microcircuits in Spacecraft," Lockheed Microelectronics Technical Note TN925, April 1979.

- Pickel, J. C. and Blandford, Jr., J. C., "Cosmic Ray Induced Errors in MOS Memory Cells," IEEE Trans. on Nuclear Science, Vol. NS-25, No. 6, December, 1978, pp. 1166-1171.

- Sivo, L. L., Peden, J. C., Brettschneider, M., Price, W., and Pentecost, P., "Cosmic Ray Induced Soft Errors in Static MOS Memory Cells," IEEE Trans. on Nuclear Science, Vol. NS-26, No. 6, December 1979, pp. 5042-5047.

- Dennard, R. H., Gaensslen, F. H., Hwa-Nieu Yu, Rideout, V. L., Bossous, E., and LeBlanc, A. R., "Design of Ion Implanted MOSFETs with Very Small Physical Dimensions," IEEE Journal of Solid State Circuits, Vol. SC-9, No. 5, October 1974, pp. 256-268.