# THE ESR BARRIER-BUCKET LLRF SYSTEM - DESIGN AND FIRST **RESULTS** \*

J. Harzheim<sup>†</sup>, D. Domont-Yankulova, K. Groß, H. Klingbeil<sup>1</sup> TU Darmstadt, Darmstadt, Germany M. Frey, D. Lens, GSI, Darmstadt, Germany <sup>1</sup> also at GSI. Darmstadt, Germany

# title of the work. publisher, and DOI Abstract

At GSI, Darmstadt, Germany, a Barrier-Bucket (BB) RF System is currently under development for the Experimental Storage Ring (ESR). The system consists of two broadband  $\stackrel{2}{\leftarrow}$  RF cavities, each driven by a solid state amplifier, with the  $\mathfrak{L}$  purpose to produce two voltage pulses per beam revolution. This will enable highly sophisticated longitudinal beam manipulations like longitudinal capture, compression and decompression or stacking of the beam. For the LLRF System, several requirements have to be fulfilled. Besides high stan-ing dards concerning the pulsed gap signal quality (e.g. ringing  $\approx 2.5\%$ ), the system has to provide the flexibility for adia-<sup>15</sup> batic voltage ramp-up and adiabatic pulse shifting with high timing accuracy. A connection to the EAIR Central Control timing accuracy. A connection to the FAIR Central Control work System (CCS) is necessary, as amplitude and phase ramp system (CCS) is necessary, as amplitude and phase ramp state will be provided by the CCS. In this contribution, the structure of the ESR BB LLRF system is presented together with experimental results from the first setup of the system. INTRODUCTION Barrier-Bucket (BB) systems enable a large variety of longitudinal beam manipulations in synchrotrons and storage

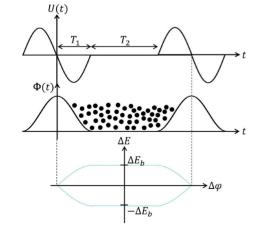

longitudinal beam manipulations in synchrotrons and storage 18 rings (e.g. [1-3]) by using pulsed gap voltages as shown in Figure 1. If the repetition frequency of the voltage pulse 0 equals the revolution frequency of the beam, this voltage Particles moving in the ring can be confined between two pulse forms a stationary potential barrier in phase space. 3.0] barriers, allowing variable bucket lengths. When the repetithis work may be used under the terms of the CC BY.

Figure 1: Single-sine voltages are used to create potential barriers in phase space, forming a bucket with maximum off-energy bucket height  $\Delta E_b$ .

Work supported by BMBF and GSI

harzheim@temf.tu-darmstadt.de

Content THPML123 tion frequency of the pulse and the revolution frequency of the particles differ, the barrier is moving in phase space ("moving barriers", e.g. [4-6]), which allows for applications like bunch merging, compression or decompression.

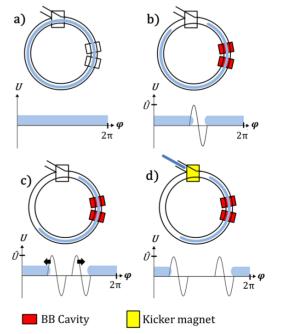

The system which is currently under development for the ESR will be used for longitudinal particle stacking [6,7]. The basic principle is shown in Figure 2. Starting with a cooled coasting beam (a), two BB pulses will be simultaneously ramped up by two BB systems, creating a gap in the beam due to the generated potential barrier (b). In the next step, the two pulses will be shifted apart, producing an empty bucket in between (c). Once this bucket is large enough, a new bunch will be injected into the empty bucket (d). In the end, the BB pulses will be ramped down, enabling the particles to merge and to form a coasting beam again. This beam will then be cooled and the stacking cycle can be repeated.

The final system will consist of two broadband RF cavities (currently, predistorted input signals contain frequencies between 900 kHz and 80 MHz), each driven by a solid state amplifier, to produce one voltage pulse per beam revolution each. In order to fullfill the high requirements on the signal quality, the LLRF system needs to be capable to store and generate predistorted input signals [8] and to flexibly control phase and amplitude of the pulses with a high accuracy.

06 Beam Instrumentation, Controls, Feedback, and Operational Aspects

rom

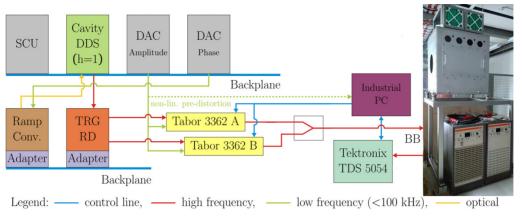

Figure 3: Schematic ESR Barrier-Bucket LLRF topology for one cavity system.

# THE LLRF TOPOLOGY

The schematic topology of the ESR BB LLRF system for one cavity system is shown in Figure 3. In a first step, the input signal needs to be calculated and stored inside the signal generators (Tabor 3362). For gap voltage amplitudes up to 550 V, the system shows linear behaviour. Thus, the system can be described by its frequency response  $\underline{H}(\omega)$ . Since the desired output signal is known and can be transformed into the frequency domain using Fourier decomposition [8], the input signal can be calculated by

$$\underline{U}_{in}(\omega) = \underline{U}_{out}(\omega) / \underline{H}(\omega).$$

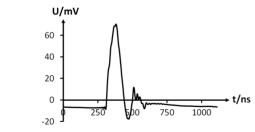

In order to measure the frequency response of the system, proper test signals are generated by the Tabor generators and the output signal is measured by the oscilloscope (Tektronix TDS 5054). Afterwards, the input signal for a certain repetition frequency (Fig. 4:  $f_{rep} = 900 \text{ kHz}$ ) is calculated by the PC and stored inside the Tabor generators.

For amplitudes above 550 V, the amplifier shows nonlinear behaviour. Therefore, the shape of the input signal needs to be changed with rising amplitude in order to generate clean BB pulses [8]. This procedure is currently investigated.

Figure 4: Predistorted input voltage signal for  $f_{rep} = 900 \text{ kHz}$ .

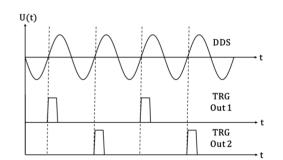

The small variation of the repetition frequency during pulse shifts might lead to conditions, where a new pulse sequence has to be started while the former sequence is still running. Thus, two Tabor Generators need to be alternately triggered. This is realized by the so called TRG module. This module receives a harmonic input signal at h=1 (revolution frequency) generated by direct digital synthesis inside the DDS module [9] and alternately produces trigger pulses at its two output ports. This is shown in Figure 5.

Any distribution of this work must maintain attribution to the author(s), title of the work, publisher, and DOI

2018).

licence (

3.0

M

the

terms of

be used under the

work may

rom this

Content

Figure 5: Input and output signals of the TRG module.

Amplitude and phase ramp data are provided to the Scalable Control Unit (SCU) by the main control room in form of tables containing the basic amplitude and phase ramp values. This table is sent to the two Digital to Analog Converters (DACs), which perform linear interpolation between the values inside the table with a resolution of 1  $\mu$ s. The output voltages of the DACs correspond to the interpolated amplitude or phase values. While the output of the amplitude DAC can be used to directly control the output voltage via the amplitude modulation (AM) functionality of the Tabor generators, the output of the phase DAC is fed into a Ramp Converter module [10]. This module controls the phase of the DDS output signal via an ODL (otpical direct link) connection and therby directly regulates the phase of the output voltage pulse.

### **MEASUREMENT RESULTS**

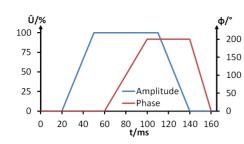

In order to test the functionality of the LLRF system, an operation with one stationary and one moving barrier using linear amplitude and phase ramps was realized in the laboratory with the real cavity. Figure 6 shows the ramps which were used in the experiment. In the beginning, no output voltage is produced. After 20 ms, the output pulses are linearly ramped up for 30 ms while the phase remains zero. The output pulses remain aligned for 10 ms and are then

T27 Low Level RF

9th International Particle Accelerator Conference ISBN: 978-3-95450-184-7

Figure 6: Input amplitude and phase ramp.

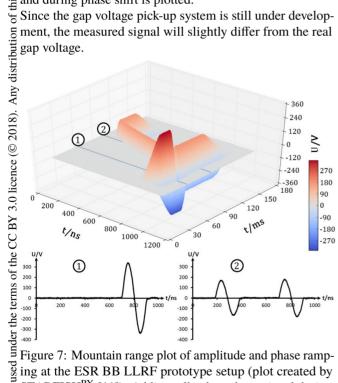

author(s), title of the work, publisher, and DOI linearly shifted for 40 ms until the phase difference amounts to 200°. 10 ms later, the amplitude of both pulses is ramped to the down to zero again in 20 ms. The level of the output signal was limited to 200 V in this measurement to make sure that was limited to 200 V in this measurement to make sure that the amplifiers remain in the linear region. The sum of the resulting gap signals is plotted in form of a mountain range plot in Figure 7. It can be seen that the requested amplitude ain and phase ramps were executed by the system. The analysis of the measured data revealed, that the phase jitter has a standard deviation of 4.29 ns which corresponds to 1.4° taking 900 kHz repetition frequency as a basis. The standard deviation of the amplitude jitter is below 1%. Additionally, work the sum of the measured gap signals during voltage ramp-up this and during phase shift is plotted.

Since the gap voltage pick-up system is still under developof

used ing at the ESR BB LLRF prototype setup (plot created by STARFISH<sup>PY</sup> [11]). Additionally, the voltage signal during é STARFISH<sup>+</sup> [11]). Additionally, the voltage signal of voltage ramp-up (1) and phase shifting (2) is shown. SUMMARY AND OUTLOOK The topology and functionality of the ESR BB LLR tem was presented and experimentally demonstrated for THPML123 06 Beam

The topology and functionality of the ESR BB LLRF system was presented and experimentally demonstrated for the

desired stacking cycle including phase and amplitude ramps. It was shown that the desired ramps are performed by the system and that a high output signal quality can be achieved. Right now, the output voltage of the system is limited to 550 V by the linear region of the amplifier.

The system is going to be installed inside the ESR this year. Therefore, the next step is to prepare the system for standard operation (e.g. configuration after power blackout). Additional functionalities like online signal optimization and a solution for nonlinear predistortion are currently developed and tested and will be added to the current system.

# REFERENCES

- [1] C.M. Bhat, "Applications of barrier bucket RF systems at Fermilab", FNAL, Batavia IL, USA, Rep. FERMILAB-CONF-06-102-AD, March 2006.

- [2] C.M.Bhat, "Barrier rf systems in synchrotrons", FNAL, Batavia IL, USA, Rep. FERMILAB-CONF-04-091-AD, 2004.

- [3] S.Y. Lee and K.Y. Ng, "Particle dynamics in storage rings with barrier rf systems", in Physical Review, vol 55, Iss. 5, May 1997.

- [4] O. Boine-Frankenheim, "RF barrier compression with space charge", in Physical Review ST Accel. Beams 13, 034202, March 2010.

- [5] M. Krestnikov, D. Steck et al., "Particle Accumulation Using Barrier Bucket RF System", in Proc. COOL'09, Lanzhou, China, 2009, paper TUM2MCIO02, pp. 67-70.

- [6] M. Steck et al., "Demonstration of Longitudinal Stacking in the ESR with Barrier Buckets and Stochastic Cooling", in Proc. COOL'11, Alushta, Ukraine, September 2011, paper TUPS20, pp. 140-143.

- [7] C. Dimopoulou et al.,"Experimental Demonstration of Longitudinal Ion Beam Accumulation with Electron Cooling", in Proc. EPAC'08, Genoa, Italy, 2008, paper WEPVA047, pp. 3470-3472.

- [8] J. Harzheim *et al.*, "Input Signal Generation for Barrier Bucket RF Systems at GSI", in Proc. IPAC'17, Copenhagen, Denmark, 2017, paper WEPVA047, pp. 3359-3362.

- [9] H. Klingbeil et al.,"New digital low-level RF system for heavy-ion synchrotrons", in Physical Review ST Accel. Beams 13, 102802.

- [10] S. Schäfer et al., "Use of FPGA-based configurable electronics to calibrate cavities", in Proc. IPAC'13, Shanghai, China, 2013, paper THPEA003, pp. 3152-3154.

- [11] D. Lens and H. Klingbeil, "A Versatile Toolchain for the Analysis of Synchrotron RF Systems? 2017 Data", LLRF'17, Barcelona, Spain, http://www.llrf2017.org/pdf/Posters/P-40.pdf

nust