# The Implementation of KSTAR Fast Interlock System using compact-RIO

# •Myungkyu Kim, Taehyun Tak, Jaesic Hong, NFRI, Deajeon, Korea

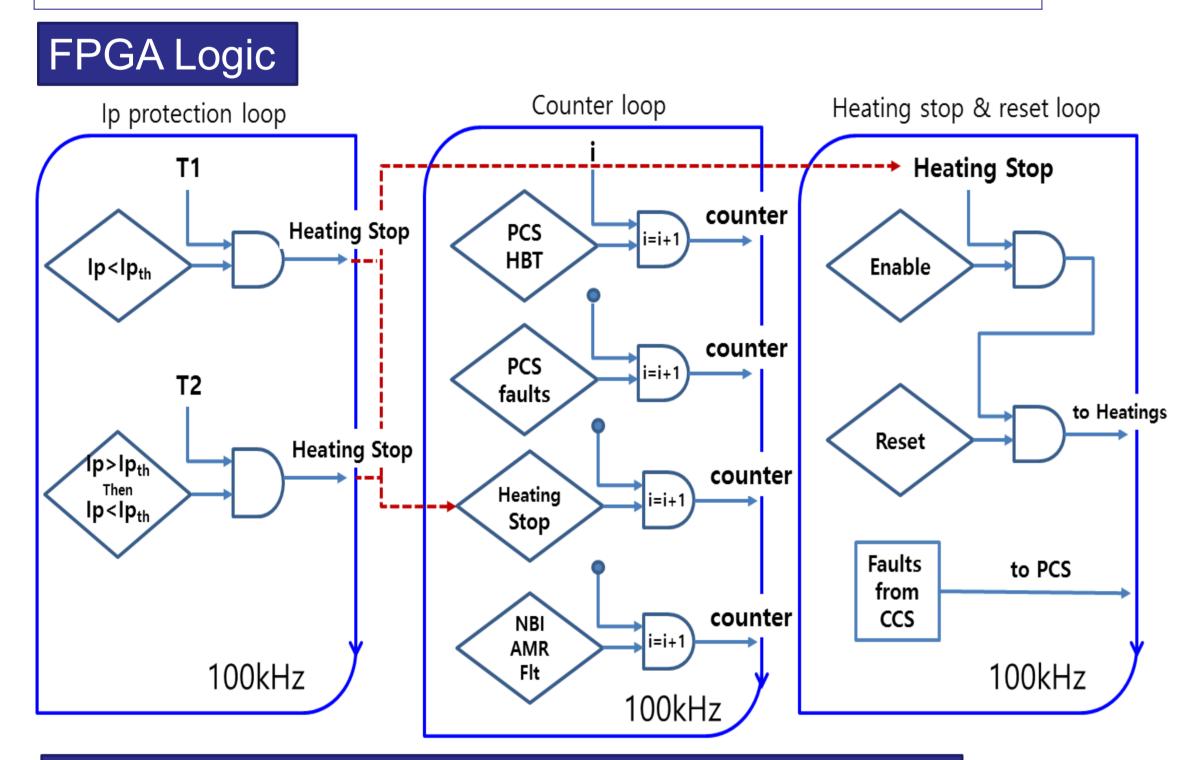

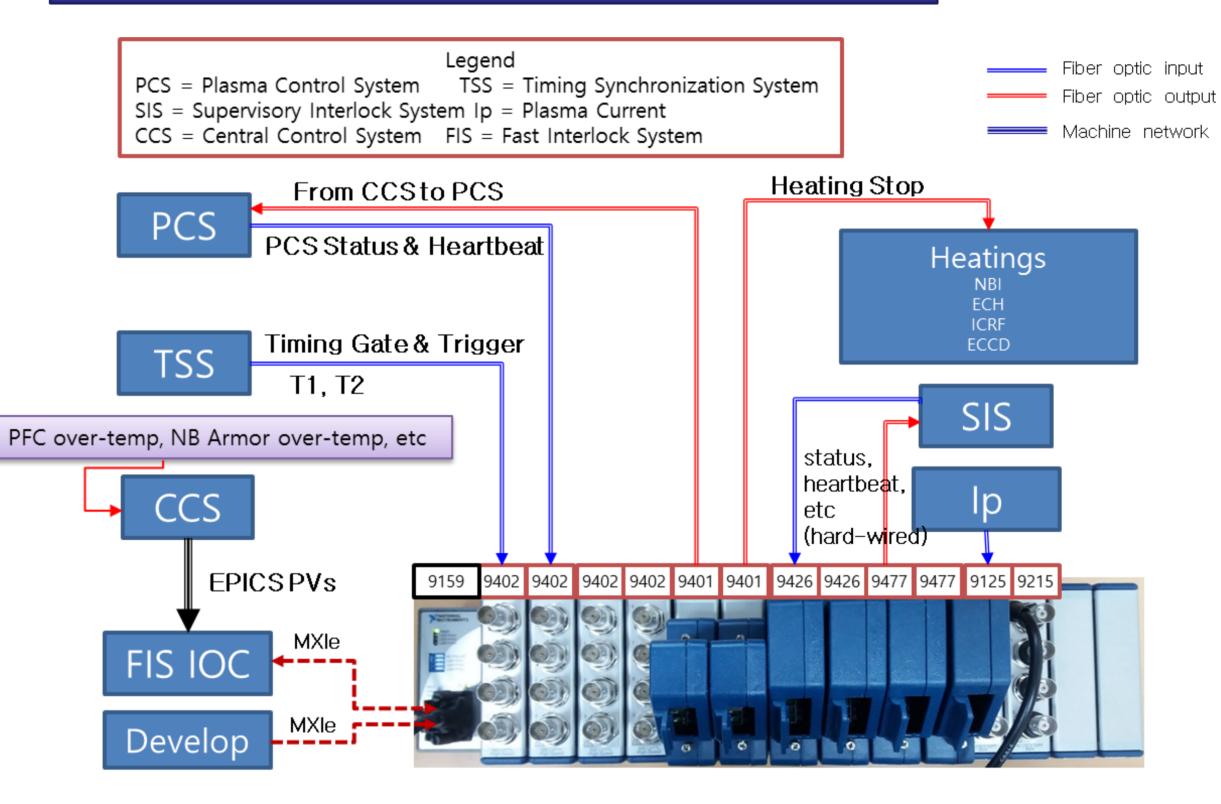

In the tokamak using superconducting magnet that can operate in long pulse with high temperature and density plasma, the interlock system is becoming more and more important to protect the device itself. Korean Super-conducting Tokamak Advanced Research (KSTAR) achieved high-confinement mode (H-mode) operation for 70 seconds in 2016. In this case, it is necessary to have precise and fast operation protection device to protect Plasma Facing Component (PFC) from high energy and long pulse plasma. The higher the energy of the plasma, the faster the protection is required, and the protection logic should be implemented to process the signals from the various devices as quickly as possible. To meet these requirements, KSTAR implemented the Fast Interlock System (FIS) using NI's Compact Reconfigurable Input Output (c-RIO). The c-RIO is a device using FPGA (Field Programmable Gate Array), its form is similar to PLC (Programmable Logic Controller) and is easy to expand I/O. The implemented protection logic is performed in the FPGA, so input and output can be processed quickly and much. The EPICS IOC performs communication with peripheral devices (PCS, CCS, SIS, heating devices) and operation of c-RIO.

• 1<sup>st</sup> Version, 2009

Central Control System (CCS) activates heating stop from Plasma Control System (PCS) using RFM within 200ms.

• 2<sup>nd</sup> Version, 2012

Fast interlock interface activates heating stop from plasma current (Ip) signal using Timing Synchronization System (TSS).

• 3<sup>rd</sup> Version, 2014

#### 2nd Version plus

Plasma Facing Component (PFC) fault, NB armor fault, CCS to PCS using RFM

#### c-RIO module description

| Modules | Description                       | No. |

|---------|-----------------------------------|-----|

| NI 9159 | 14-slot chassis, LX110 FPGA, MXIe | 1   |

| NI 9402 | 4-ch, 55ns, DIO, BNC              | 4   |

| NI 9401 | 8-ch, 100ns, DIO, 25pin D-SUB     | 2   |

| NI 9426 | 32-ch, 7#s, DI, 37pin D-SUB       | 2   |

| NI 9477 | 32-ch, 8µs, DO, 37pin D-SUB       | 2   |

| NI 9215 | 4-ch, 100kS/s/ch, 16 bit AI, BNC  | 2   |

- Fast response time, fast processing time

- Proven device, platform, high reliability

- Easily implement and modify logic using FPGA and LabVIEW

- Fast system development

- Communication with EPICS using IRIO is possible.

### Configuration of KSTAR fast Interlock System

## Conditions for fast Interlock

#### Test result for the Counter loop(heartbeat error)

#### PCS Heartbeat(HBT) error forced generation

| 🗵 root@fastIOC:/usr/local/epics/siteApp/fisIOC/iocBoot/iocfisIOC (on fastIOC) _ 🗆 🗙 | auxDO105 : T2, True = ON       |

|-------------------------------------------------------------------------------------|--------------------------------|

| File Edit View Search Terminal Help                                                 | auxDO7 : reset, True = ON      |

| FIS-SRV-HWCF:NI9159-0-auxD07 2017-04-17 11:14:51.411684 TRUE                        | auxDO100 : HBT error, False=ON |

| FIS-SRV-HWCF:NI9159-0-auxD07 2017-04-17 11:14:54.674846 FALSE                       |                                |

| FIS-SRV-HWCF:NI9159-0-auxD0105 2017-04-17 11:15:11.909170 TRUE                      |                                |

| FIS-SRV-HWCF:NI9159-0-auxD0100 2017-04-17 11:15:28.782058 FALSE                     |                                |

| FIS-SRV-HWCF:NI9159-0-auxAI7 2017-04-17 11:15:28.790971 1.68748e+06                 |                                |

| FIS-SRV-HWCF:NI9159-0-auxD0105 2017-04-17 11:15:53.653142 FALSE                     |                                |

| FIS-SRV-HWCF:NI9159-0-auxD07 2017-04-17 11:15:58.708233 TRUE                        |                                |

| FIS-SRV-HWCF:NI9159-0-auxD07 2017-04-17 11:16:01.652333 FALSE reset1                | T2 ON, HBT error               |

| FIS-SRV-HWCF:NI9159-0-auxD0100 2017-04-17 11:16:19.796365 TRUE                      |                                |

| FIS-SRV-HWCF:NI9159-0-auxD0105 2017-04-17 11:16:48.773114 TRUE                      | =>2.111698 sec                 |

| FIS-SRV-HWCF:NI9159-0-auxD0100 2017-04-17 11:16:50 884812 FALSE action1             | <u>Counter</u> = 2,11369 sec   |

| FIS-SRV-HWCF:NI9159-0-auxAI7 2017-04-17 11:16:50.890941 211369                      | ∆t = 0.001992s                 |

| FIS-SRV-HWCF:NI9159-0-auxD0100 2017-04-17 11:17:14.853237 TRUE                      |                                |

| FIS-SRV-HWCF:NI9159-0-auxD0105 2017-04-17 11:17:23.045226 FALSE                     |                                |

| FIS-SRV-HWCF:NI9159-0-auxD07 2017-04-17 11:17:32.310262 TRUE                        |                                |

| FIS-SRV-HWCF:NI9159-0-auxD07 2017-04-17 11:17:35.461246 FALSE reset2                | T2 ON, HBT error               |

| FIS-SRV-HWCF:NI9159-0-auxD0105 2017-04-17 11:18:03.912902 TRUE                      | =>1,565027 sec                 |

| FIS-SRV-HWCF:NI9159-0-auxD0100 2017-04-17 11:18:05.477929 FALSE action2             | Counter = 1,56702 sec          |

| FIS-SRV-HWCF:NI9159-0-auxAI7 2017-04-17 11:18:05.490945 156702                      | ∆t = 0.001993s                 |

| FIS-SRV-HWCF:NI9159-0-auxD07 2017-04-17 11:18:14.886126 TRUE                        |                                |

| ETS_SRV_HWCE.NT0150_0_2UXD0105_2017_04_17_11.18.10_043770_EALSE                     |                                |

- While T1 ON, Ip<Ip<sub>th</sub>

- While T2 ON, Ip>Ip<sub>th</sub> then Ip<Ip<sub>th</sub>

- PCS fault

- NBI armour over-temperature fault via EPICS

- PFC over-temperature fault via EPICS

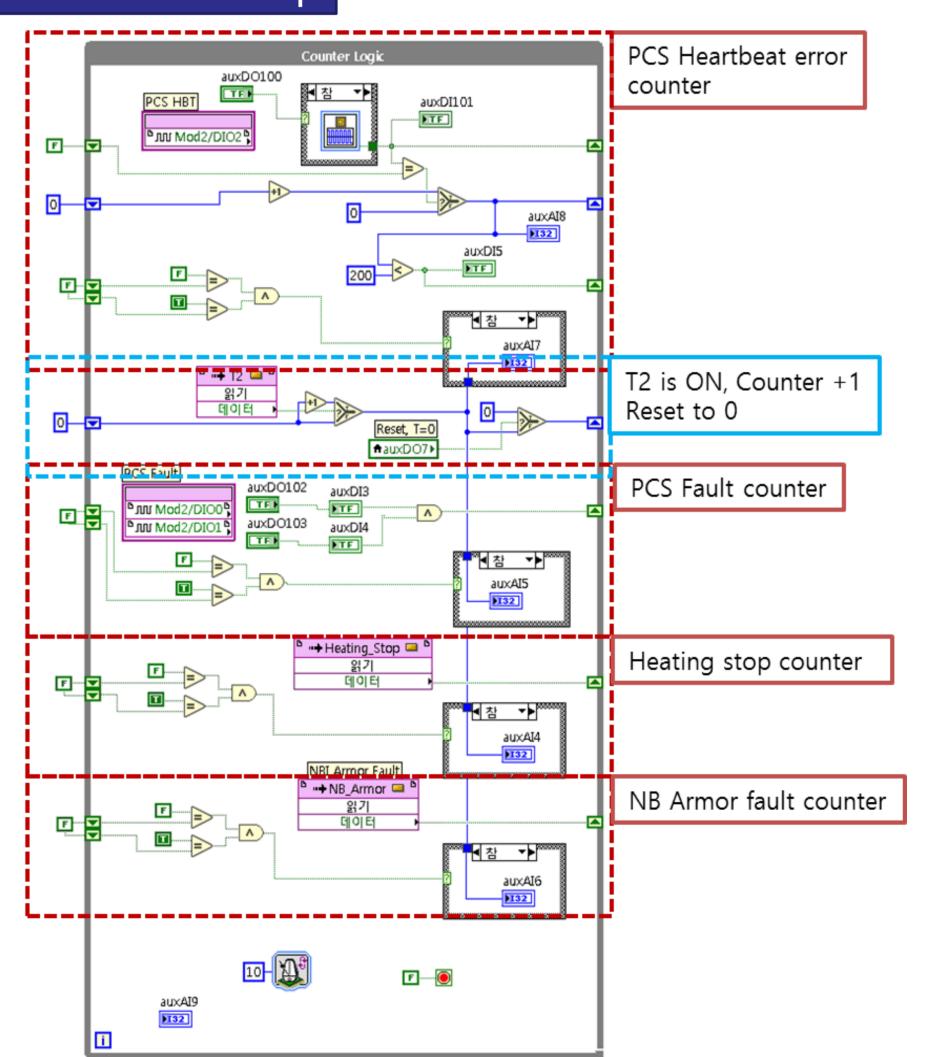

#### LabVIEW FPGA code for the Counter loop

Counter Loop(Logic) Event recording after T2 ON Increase counter 1 by 10<sup>µs</sup> cycle

auxAl4 : Heating stop counter auxAl5 : PCS fault counter auxAl6 : NBI Armor fault counter auxAl7 : PCS Heartbeat error(1kHz) counter

FIS-SRV-HWCF:NI9159-0-auxD0105 2017-04-17 11:18:19.943779 FALSE FIS-SRV-HWCF:NI9159-0-auxD07 2017-04-17 11:18:25.189839 FALSE FIS-SRV-HWCF:NI9159-0-auxD0100 2017-04-17 11:18:30.165815 TRUE

HBT fault occurs when the same value exceeds 200 times during 1 kHz HBT at 10 µs clock.

Theoretically, 1st detection is possible only after 2ms!

**Conclusion & Future works**

- 4th version The KSTAR Fast Interlock System was installed hardware and software for 2017 operation.

- However, due to the early termination of the unexpected campaign, commissioning on actual equipment had to be delayed until 2018.

- FPGA programming is preparing for more features and a variety of situations, and will be applied in 2018.

- Also, in the long term, Fast Interlock Server will share information with PCS and RFM Gate-way using Synchronous Databus Network (SDN) of ITER.