# MULTIPURPOSE LLRF FIELD CONTROLLER FOR VARIOUS SUPERCONDUCTING CAVITY APPLICATIONS

Wojciech Cichalewski, Wojciech Jalmuzna, Dariusz Makowski, Andrzej Napieralski TUL-DMCS, Lodz, Poland

# Abstract

Superconducting cavities are widely used as accelerating structures, especially for FEL experiments [4]. Even in a single project, the cavities are used in many different systems. Therefore multiple applications require not only different cavity parameters (such as loaded Q, bandwidth, resonance frequency) but also specific modes of operation (pulsed, CW). The paper presents the implementation of multi-purpose LLRF field controller suitable for large span of such systems. It is implemented for reconfigurable FPGA chips and can be used with various hardware platforms. Implementation issues are described together with operation experience in such facilities as FLASH [2].

# **INTRODUCTION**

The linear accelerator facilities based on the superconducting technology differ in terms of executed experiment type, but for all of them, the quality of the results of performed experiments is strongly correlated with the energy stability of the provided electron beam. This stability depends on the several factors connected to different components of the accelerator, but the most important is the quality of the accelerating RF (Radio Frequency) field. To minimize field's amplitude and phase fluctuations LLRF (Low Level Radio Frequency) control system is used [3],[4]. Its task is to measure electromagnetic field inside accelerating structures, compare it with a required value, and adjust an output of an RF field source accordingly to ensure required field stability[1]. The central element of the system is a controller capable of executing chosen transfer function. In former projects, the controller was implemented as analog system, but during last years, the digital implementations are becoming more popular. In addition to the controller, the digital LLRF system is also equipped with down-converters - to provide high frequency signals demodulation for sampling with low frequency ADCs (Analog to Digital Converter) - and up-converters - to prepare drive signal for RF amplifier chain [5].

# **CONTROLLER REQUIREMENTS**

The analysis of several existing LLRF control systems and executed algorithms shows, that they share many common elements on each level of complexity. This provides the possibility to create universal, digital application, which can be used to control parameters of RF accelerating field in various system configurations and under different work conditions. The parameters considered during LLRF controller development are described in the following sections.

#### Reconfigurable Hardware

# Hardware Platform

The controller must offer the wide range of functionality. In addition, it must be possible to use it in wide range of different digital systems. The most flexibility (in system configuration) is offered by FPGA chips, therefore they are commonly used in different LLRF control systems.

# Communication Interface

Different hardware systems require different communication protocols. The controller application must be equipped with extendible communication module which supports commonly used protocols (like: VME, Ethernet, PCIe) and allows users to add support for additional ones.

### Transfer Function

Different mode of operation, type of accelerating structures and requirements may need different transfer functions executed by the controller. It must support basic functions such as P-controller, PI-controller and PID-controller, but also give the possibility to adjust the transfer function according to the user needs.

# Executed Algorithm

The different requirements for executed algorithm include the number of cavities connected to the system and their parameters, intermediate frequency used by downconverters, latency requirements and numerical precision. The controller must provide appropriate structure to fulfil all these needs using available computation power.

### Frequency Tuning

Narrow bandwidth of the cavities, especially for high Q ones, requires special considerations while loading to and maintaining required RF field level. The controller must provide the possibility to change output frequency of the vector modulator or upconverter used. This will allow to match the driving frequency to the current resonance frequency of the cavity, therefore it will make the loading process possible even for large frequency offsets.

### Mode of Operation

Due to the different requirements for LLRF control systems, the controller must support different modes of operations. This include GDR (Generator Driven Mode), SEL (Self Excited Loop) and VCO (Voltage Controller Oscillator). Each mode can be operated as either pulsed or CW (Continuous Wave).

### **COMPUTATION MODULES**

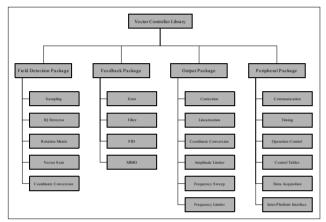

The computation modules have been implemented using VHDL language. They are using either saturated or overflow arithmetic depending on the requirements. They have large number of design-time and run-time parameters, which allow to customize components configuration according to user needs. The modules have been grouped into Vector Component Library. The structure of the library (see Figure 1) and the flexibility of individual modules make the library universal tool for design of signal processing applications based on the FPGA technology. The parts of the library have been used during the implementation of several algorithms running currently at FLASH facility.

Figure 1: The structure of the Vector Controller Library.

### **OPERATION CONTROL MODULES**

Different modes of operation varying from pulsed to CW require special support from DAQ subsystem, communication subsystem and control parameter generation subsystem. For that purpose, special set of modules has been prepared. It includes programmable generators, function interpolators, memory controllers etc. Together with computation modules they allow to execute wide range of control algorithms.

### HARDWARE PLATFORM SUPPORT

To provide support for multiple hardware platforms, special controller framework has been prepared. It separates functionality of the controller from the routines for handling hardware peripherals such as memories, communication links and external supporting processors. The user must prepare special set of configuration files for target platform and provide dedicated peripheral drivers if necessary. The controller already includes support for platforms used at FLASH - VME based distributed system equipped with FPGA chips and ATCA based platform [6].

### HIGH LEVEL APPLICATIONS SUPPORT

Several high level applications (HLA's) have been developed in order to support and evaluate LLRF

controller operation. These applications are implemented as middle layer DOOCS (Distributed Object Oriented Control System) servers or as Matlab scripts, which perform data exchange with the DOOCS environment. As far as this applications are implemented in higher hardware level, its response time cannot be strictly determined. That is why the high level applications are not restricted to intra-pulse operation (for pulsed LLRF facilities).

Depending on the functionality delivered by the applications, they have been divided into two main groups: diagnostic and control. The control algorithms family includes: redundant feed forward (simple FF signal generation), adaptive feed-forward (pulse-to-pulse FF signal correction due to estimated repetitive errors), cavity frequency tuning (slow and fast control with step motors and piezo tuners), cavity parameters estimation, High Power Amplifiers Chain (HPAC) linearization etc. As an examples of diagnostic HLA's one can mention: RF components characterization, vector sum calibration, operation limits estimation, power budget determination, HPAC characterization, and others.

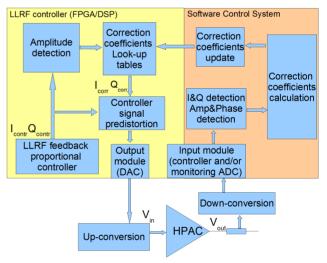

The part of applications require dedicated support on the controller side. One of such applications is the HPAC linearization solution bases on the digital predistorter. The set of HLA determines non-linear transfer functions of amplifiers and calculates correction coefficients for control signal shaped by the LLRF controller.

Figure 2: Block diagram of the HPAC linearization implementation.

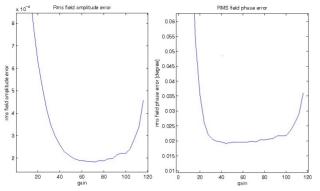

The example of diagnostic HLA is a tool for optimal feedback gain or loop gain and loop phase evaluation. The first application is used for measurement of loop error signal in function of the feedback gain. The information gained from both applications is used for the loop parameters optimization (optimal gain, gain tables scheduling, etc.).

Figure 3: Feedback loop gain study in one RF station of FLASH facility.

#### **IMPLEMENTATIONS**

The presented solution has been applied in several facilities. The following subsections present the results of measurements performed in FLASH laser and Vertical Test Stand.

#### FLASH

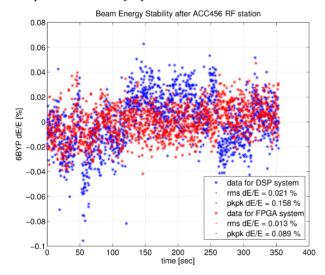

The superconducting linear accelerator, which is part of FLASH facility, is working in pulsed mode using single RF field source (klystron) to drive 8-24 cavities. The presented controller has been installed and used to drive several RF stations using distributed VME based system. Figure 4 presents beam energy stability comparison between old generation DSP control system and FPGA based one. The application of presented solution allowed to improve the stability by a factor of 2.

Figure 4: Beam energy stability measured using old DSP system and new FPGA based one.

### Vertical Test Stand

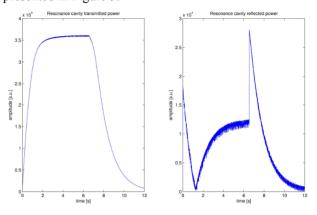

The controller has also been used in Vertical Test Stand at DESY to drive single superconducting cavity during conditioning and initial characterization measurements. Due to the special coupling, the loaded Q of the cavity is in range of  $10^9$ . The dedicated modes of operation such as SEL and VCO, which allow precise resonance frequency

Reconfigurable Hardware

tracking has been used to drive each of the cavity passband modes. The results of the measurements are presented in Figure 5.

Figure 5: Transmitted and reflected power signals during High Q cavity operation at VTS facility.

#### SUMMARY

The LLRF Controller presented in the paper can be used with the accelerating structures characterized by different parameters and modes of operation. The test results for different accelerator facilities and hardware architectures proved its flexibility. The Controller can be easily extended by additional modules to accommodate new solutions, field control concepts and algorithms, but also changes and extensions to the hardware platform. The solution has been proposed and will be used as a base for XFEL controller.

#### ACKNOWLEDGEMENT

The research leading to these results has received funding from the European Commission under the EuCARD FP7 Research Infrastructures grant agreement no. 227579

The author is a scholarship holder of project entitled "Innovative education ..." supported by European Social Fund.

#### REFERENCES

- [1] A. Brandt, LLRF Systems for Modern Linacs: Design and Performance, LINAC06 Proceedings.

- [2] V.Ayvazyan et al. Hardware and Software Design for the DSP Based LLRF Control, PAC2005 Proceedings.

- [3] M.Champion et al., Overview of the Spallation Neutron Source Linac Low-Level RF Control System, PAC05 Proceedings, DOI:0-7803-8859-3/05.

- [4] R. Brinkmann et al., TESLA Technical Design Report Part II: The Accelerator, DESY 2001-011, ECFA 2001-209, 2001.

- [5] S. Simrock et al., Universal Controller for Digital RF Control, EPAC2006 Proceedings, TUPCH190.

- [6] S. Simrock et al., Evaluation of an ATCA Based LLRF Control System at FLASH, Mixdes 2009.