© 1985 IEEE. Personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works must be obtained from the IEEE.

IEEE Transactions on Nuclear Science, Vol. NS-32, No. 5, October 1985

# MULTI-PROCESSOR CONTROL OF THE 100 KeV MCMASTER MARK IV SPUTTER ION SOURCE\*

W. F. S. Poehlman, Institute for Materials Research

R. J. Pollock, Department of Engineering Physics\*\*

R. A. McNaught, Tandem Accelerator Laboratory

McMaster University

Hamilton, Ontario Canada L8S 4M1

### Abstract

An ion source control system has been developed to provide 100 KeV heavy ion injection into the McMaster FN Tandem. The control system is composed of a CMOS RCA1802 microprocessor at deck potential which conveys power supply command/status data from/to a PDP-11/23 via fibre optic link. Approximately 50 fail safe interlock conditions are maintained by the PDP with capabilities to shut down affected power supplies if interlock states warrant. There are commands that allow operator intervention to set supply voltages, source cone position, and interlock bypass. Power supply set point voltages are either maintained to within modifiable regulation windows, or set to track manually controllable shaft encoders. The ion source status is provided to the operator from the PDP via a DEC VT220 monochrome display terminal and printer. There are two possible display modes, both with variable updates rates; one involving power supply voltage/current information and interlock status, and one indicating abnormal stati caused by cascading failed interlocks. An additional serial line on the PDP-11/23 allows user communications, including a "screen dump" of any of the displays, to a remote location through the use of a 1200 baud modem.

#### Introduction

A computer controlled ion injection source system for McMaster University's tandem accelerator has been The control system is now complete[1] with developed. ion source construction well underway. Within the Accelerator Laboratory, there are already in use several ion sources including sputter, tritium and polarized. The latter source being operated at 50 KV deck potential by manual operator control with lucite rod isola-The new ion injection source system has been tion. developed with computer control. Operator commands can now be given from the control room on a PDP-11 terminal keyboard. They are then implemented by a microprocessor at ion source deck potential. In planning this system, the following design goals were formulated:

- Short (2 character keystrokes) but descriptive commands needed for operator control;

- Computer controlled interlocks to avoid improper operator action and to minimize damage due to component failure;

- Several display modes to convey source operation and interlock status;

- The provision of more conventional control knobs in order to continuously vary selected power supply parameters for beam optimization (steering);

- The inclusion of power supply regulation duties for the control computer;

- The possibility of remote location communication.

# Hardware Description

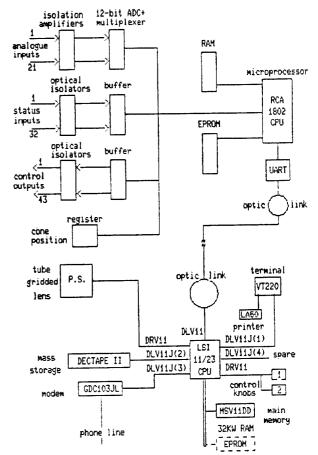

The design of the hardware system, normally susceptible to larger static voltage discharges, pays particular attention to robustness through the suitable utilization of isolation devices and, on the deck, a CMOS microprocessor with high noise immunity[2] as shown in Figure 1. The detection of 21 analogue signals including power supply currents and voltages, temperatures and vacuum pressures, is accomplished through isolation amplifiers. The 32 digital signal sensors or inputs and the 43 control outputs are buffered between microprocessor and device by optical isolators.

FIGURE 1. Ion Source Control System

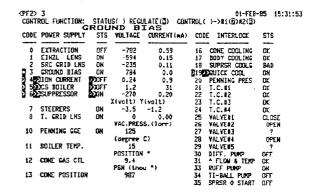

Figures 2(a) and (b) show device parameters displayed and interlocks controlled while Table One lists controlled power supplies and the ADC conversion gain being used for monitoring. All power supplies were modified to operate from motor driven variacs. Some supplies also allow fine or vernier control as well as coarse voltage control. The up/down link between the I/O processor at deck potential and the PDP-11/23 at ground potential uses a fibre optic serial line.

The PDP-11/23, initially a LSI-11/2 CPU which proved too slow to regulate power supplies without oscillation (hunting), utilizes four serial lines and two parallel interfaces. As illustrated in Figure 1, the fibre optic link to the RCA1802 is on a separate interface. For reasons outlined in the next section, it is necessary to give priority to the communiction with the RCA1802 over terminal I/O operations by certain positioning of these devices on the PDP-11 backplane. (The four serial line unit (DLV11-J) does not allow internal selectable interrupt priority). The user control knobs utilize shaft angle encoders whose digitized results are placed in one parallel line unit

2083

(DRV11) register for read only operation. The other parallel line unit serves as a read/write register for the tube gridded lens power supply, at ground potential, which has an internal regulation and voltage settable system.

# Table One

# ICN SOURCE POWER SUPPLY COMPLEMENT

| Source Power Supply Systems                            | ADC Reading Resolution                                       |  |  |  |

|--------------------------------------------------------|--------------------------------------------------------------|--|--|--|

| Cs. Boiler (O to 50Vac)                                | Voltage – 8 bits<br>Current – 8 bits                         |  |  |  |

| Ionizer Current (O to 10Vac)                           | Voltage - 8 bits<br>Current - 8 bits                         |  |  |  |

| Suppressor (O to -3kVdc)                               | Voltage - 8 bits<br>Current - 8 bits                         |  |  |  |

| Extraction (O to -32kVdc)                              | Voltage - 10bits<br>Current - 8 bits                         |  |  |  |

| Cs Einzel Lens (O to -32Vdc)                           | Voltage - 10bits                                             |  |  |  |

| Ground Bias (O to 5kVdc)                               | Current - 8 bits<br>Voltage - 8 bits                         |  |  |  |

| Source Gridded Lens 90 to -10kVc                       | ē                                                            |  |  |  |

| Steerers, X and Y (-1kV to +1kV                        | Current - 8 bits<br>dc) Voltage - 8 bits<br>Current - 8 bits |  |  |  |

| and at ground potential:                               |                                                              |  |  |  |

| Deck (O to -100kVdc)<br>Tube Gridded Lens (O to -32 kV | not connected                                                |  |  |  |

#### Software Considerations

Program development for both the RCA1802 deck microprocessor and the LSI-11/23 ground potential processor was done on a TSX+ multi-user[3] PDP-11/23. For the RCA1802, a cross assembler was utilized and since the duties of the deck processor were relatively straight forward, object code output was implemented directly into EPROM. The tasks for the control program include interrupt driven input (from the LSI-11/23) and an ASCII dump of ADC 12-bit conversion data (25 microsecond successive approximation type[4]) from the various analog signals with digital binary data for device stati. As simple as the RCA1802 code is, the LSI-11 code proved to be far more complex.

One of the prime considerations in the PDP-11 control program development is speedy and efficient performance. Without this, power supply regulation duties could not adequately be carried out in addition to other tasks such as interlock monitor and control, and terminal display updates and communications with the deck microprocessor (RCA1802). About 90% of programming was done in the MACRO assembly language[5]. A higher level language[6], FORTRAN 77, was utilized for floating point calculations (converting ADC units to voltages, currents and pressures, etc.) and formatted display output subroutines once the screen cursor was correctly positioned. For program development purposes, the program was edited, compiled and linked on the DEC PDP-11/23 multi-user RT11 Operating System, copied to TU58 tapes and transported to the site PDP-11, running RT11 foreground/ background system with DECTAPE II. Although slow to load (2.50 minutes), the program was much more easily modified than would be the case with an EPROM committed program. The code was so structured, however, so as to be amenable to EPROM operation with a small RAM requirement.

Early on, it became apparent that the display screens, using direct cursor addressing, required half of the processing time in the PDP-11. The regeneration of the RT11 operating system incoporating high speed ring buffers and terminal handlers reduced this task to under a quarter of total time requirements. Although all input/output was handled with suitably prioritized interrupt completion routines, the hardware priority in serial line operation still had to be given to communications with the deck control processor. This necessitated a dedicated serial line for the RCA1802 as shown in Figure 1. Two displays were developed, one to indicate operating parameters (see Figure 2(a)) and one to detail interlock configurations (see Figure 2(b)). In both cases, only changed information is written to the screen unless a new display is selected which requires a complete screen rewrite.

FIGURE 2(a). Screen dump of the terminal main display.

| (PF1> 4                                               |                        |                                                                 | INTERLOCKS         | 01-FEB-85 15:39:44                                                                 |

|-------------------------------------------------------|------------------------|-----------------------------------------------------------------|--------------------|------------------------------------------------------------------------------------|

| NO. DEVICE                                            | STS                    | INTERLOC STS                                                    | ENABL   NO. DEVICE | STS # INTERLOC STS ENABL                                                           |

| 0 EXTRN PS                                            | OFF                    | 0 PNG VAC DK<br>1 CONE CL DK<br>2 BODY CL DK                    | YES I              | ON 0 SUP (500Y OK YES<br>OFF 0 T.C. #3 BAD YES<br>1 T.C. #4 OK YES                 |

| 1 EINZL LN<br>2 S GRD LN<br>3 GRND BI                 | dh<br>Cn<br>Chi        | 3 VALVE #2 BAD<br>0 PNG VAC OK<br>0 PNG VAC OK<br>0 PNG VAC DK  | YES I              | OFF O T.C. H2 OK YES<br>1 T.C. #3 BAD YES<br>2 VALVE #5 BAD YES                    |

| 4 IONIZER                                             | OFF                    | 0 PNG VAC DK<br>0 CONE CL OK<br>1 BODY CL OK<br>2 SUP>500V BAD  | YES I              | DFF 0 T.C. 11 DK ND<br>1 T.C. 13 BAD YES<br>DFF 0 T.C. 12 DK YES                   |

| 5 CS BOILR<br>6 SUPPRESS<br>7 STEERERS<br>10 PNG CAGE | off<br>on<br>dn<br>dft | O RUICK CL BAD<br>O PNG VAC DK<br>O PNG VAC DK<br>O T.C. NJ BAD | YES I<br>YES I     | I DIFF FLO OK YES<br>2 DIFF TMP OK YES<br>3 RUFF PMP OK YES<br>DFF 0 T.C. #1 DK NO |

FIGURE 2(b). Screen dump of the terminal interlock display.

The RCA1802 deck processor, and the PDP-11/23 main processor, intercommunicate via ASCII strings. In order to operate with low timing overhead, only minimal handshaking or error retries are performed. Errors detected include receiver hardware checks involving parity, framing and overrun conditions. As explained below only one type of retry is done. Upon command, the RCA1802 reports the status of the source devices via a 30 byte packet. If the PDP-11 verifies that it has successfully received 30 bytes, processing begins, otherwise a "report" command is reissued from the PDF-11 to the RCA1802. When a control request, such as "extraction voltage up", is necessary, the PDP-11 sends the device code (the RCA1802 memory-mapped location for that device register) and the appropriate control bit pattern for the device command and status register. If the RCA1802 detects a receiver error, no action on the PDP-11 request is taken. The PDP-11 will reissue the request as part of the duties of the next processing loop operation.

One of the more time critical tasks for this system, is the regulation to better than 3 percent of power supply voltages. Some supplies require better regulation than others, so that the PDP-11 program allows user variable regulation "windows" or trigger levels. Beyond these floor and ceiling values, a voltage cannot stray without the PDP-11 issuing a command to the RCA1802 to lower or raise the voltage as required. Another advantage to programmable regulation is the ability to minimize voltage hunting which varies from supply to supply depending on variac motor speed, fine or coarse level control, or differing noise levels on the feedback lines. Another important duty of the PDP-11 is to perform logic tests to determine if component failures are present and to take corrective action by closing values, or power supply shutdown. If a situation warrants, any interlock may be 'bypassed' or made 'active' via operator command. In bypass mode, abnormal conditions are marked on the main display via reverse video writing while, in active mode, flashing reverse video is utilized, designated supplies are deactiviated and bells ring when an abnormal condition is detected.

The lowest priority task of the PDP-11 system is to process user keyboard input. Commands include the ability to turn supplies ON or OFF, set voltage levels, both by user input value or by control knob attachment and rotation, change valve positions, change interlock conditions and select displays. These operations are accomplished by 2 character keystrokes, the first being a special function key and the latter being a numeric device code as shown on the display. If special function key n (PFn) is not depressed, then the ASCII string which follows for up to 80 characters is simply reproduced on the command line for logging purposes during remote screen dumps or printer outputs. Table Two summarizes the user input commands. When any command is successfully completed, the display will reflect some change.

#### Table Two

#### USER INPUT COMMANDS

| Special     | Function Keys | Operation Performed          |

|-------------|---------------|------------------------------|

|             |               | ·····                        |

| (PF1) code  | Change s      | tatus or device "code" to    |

| STATUS      | "sta          | tus"                         |

| (PF2) code  | Change p      | resent voltage for device    |

| VOLTS       | "cod          | e" to "volts"                |

| (PF3) code  | Connect       | device "code" to a control   |

| 1 or 2      | knob          | number "1 or 2"              |

| (PF4)       | Change t      | o interlock display          |

| ^T(cntrl T) | Enable rem    | ote communication(Talk) mode |

| ^E(cntrl E) | Exit remot    | e communication mode         |

| ^D(cntrl D) | Perform so    | reen dump in ASCII string    |

|             | form          | to remote location.          |

For example, Figure 2(a) shows an asterisk at the left of device 3 which has been preset to a regulation voltage (note the asterisk in the regulate column at line 2) via the command (PF2). It also shows an interlock violation -- the Quick Cool which affects three power supplies: lonizer current, Cs Boiler, and suppressor, all flagged in reverse video as well. If the quick cool interlock is active (enabled) as shown in Figure 2(b) then this reverse video on the main display would be flashing, bells would be ringing, and the three affected power supplies would be shutdown via computer command. If the interlock was bypassed (not enabled) then no bells or supply shutdowns, only steady reverse video would be present. If a user keystroke is in error, then a "?" appears in place of the user echoed characters which indicate no operation was performed.

A special mode, invoked by the CNTRL T simultaneous keypress, allows input/output to be performed using one of the PDP-11 serial lines. This includes a screen dump of either of the two possible displays which is sent sequentially as 24 lines of 80 characters each. When connected to a modem, an "on-call" technician with any dumb terminal can type to the last line on the screen with up to 80 characters. Any user keyboard input in this mode is echoed on the top line of the screen as well as sent as output through the modem to the remote terminal. When ready, a CNTRL D keypress sends the currently displayed screen contents to the remote terminal for evaluation. The CNTRL E command will exit the talk communication mode. Note that under this mode, all control operations are unaffected being performed with a higher priority.

# Control System Operation

A full test of all supplies and switch simulated interlock failures has resulted in the following performance figures. The DEC VT220 terminal, operating at 9.6K baud performs a complete screen rewrite in under one second. Screen updates, performed at every 10 processing loop passes, occur at better than every second of elapsed time. Under full load, constituted by all supplies regulating at preset voltages and the system in remote talk mode, the processing loop requires about 20 percent increase in time for completion, that is, moving from 50 milliseconds to 60 milliseconds. Supplies can be regulated to within 0.5 percent. This compares favourably with the regulation obtained in the tube gridded lens supply which contains internal regulation electronics. Use was initially made of a slower main processor, the LSI-11/2 CPU which revealed that regulation could not be obtained to better than 2% without severe hunting effects. The PDP-11/23 control program currently occupies 14K 16-bit words out of a possible 28K words, leaving 14K words for expansion.

#### Conclusions

The computer control systems developed at McMaster for the Heavy Ion Injection Source has performed adequately in power supply control, interlock monitoring, and providing a palatable user command and status interface. "Luxury facilities" such as hardcopy logging output and remote location communication are implemented without undue effect on program performance. The modular construction of the program allows ready inclusion of more devices and interlocks. Program size is one-half of total memory available, allowing much free space for expansion of the program with additional devices and features.

#### References

- R.J.Pollock, <u>Computer Controlled Ion</u> <u>Injection Source System</u>, M.Eng.Thesis, McMaster University, Department of Engineering Physics, (Hamilton, Ont.-- 1985).

- RCA Solid State, <u>COS/MOS</u> <u>Memories</u>, <u>Microprocessors</u>, and <u>Support Systems</u>, (Sommerville, N.J.-- 1978).

- S & H Computer Systems, Inc., <u>TSX-Plus</u> <u>Reference</u> <u>Manual</u>, Version 5.0, (Nashville, <u>Tenn.--</u> 1984).

- 4. Analogue Devices, <u>Integrated</u> <u>Circuit</u> <u>12-Bit Analogue to Digital Converter</u> (Norwood, Mass.-- 1978).

- Digital Equipment Corporation, <u>RT11 Manual</u> Set, Version 5.0, (Maynard, Mass. -- 1982).

- 6. Digital Equipment Corporation, FORTRAN77/RT11 Manual Set, Version 5.0, (Maynard, Mass.-- 1984).

\* Work supported by the Natural Sciences and Engineering Research Council of Canada. \*\* Present Address: Northern Telecom, Belleville, Ontario, Canada.