© 1985 IEEE. Personal use of this material is permitted. However, permission to reprint/republish this material

for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers

or lists, or to reuse any copyrighted component of this work in other works must be obtained from the IEEE.

IEEE Transactions on Nuclear Science, Vol. NS-32, No. 5, October 1985

#### BEAM PROFILE MONITOR SYSTEM FOR THE BEVALAC TRANSFER LINE\*

Greg Stover Lawrence Berkeley Laboratory University of California Berkeley, CA 94720

# <u>Abstract</u>

Incorporated in the current Bevalac transfer line upgrade project is a proposal for a new electronic beam monitoring system. It will be designed to amplify, convert, and transmit the signals of twelve 16 by 16 multi-wire grids to a central computer located in the Bevatron control room. Each station will contain interface amplifiers and a local microprocessor to convert wire grid currents into digitized values which will then be transmitted via a serial data channel to the main computer. The system will have a large dynamic range (1 nano to 1 milli-ampere of beam current), be designed for will operation, distributed and be easily This paper will describe the basic expandable. electronic hardware and software components of the proposed system.

## Introduction

In 1974 a transfer line linking the SuperHILAC to the Bevatron was completed, forming the Bevalac System.[1] With a vacuum in the low 10-6 torr range beams up to 56 Fe could be accelerated. By 1982 the vacuum in the Bevatron was improved to better than 10-10 torr permitting the acceleration of relativistic Uranium ions.[2] Unfortunately due to the physics of the Penning Ion Gauge (P.I.G.) source employed at this facility, ion current intensities generally decrease in proportion to the square root of their atomic mass. Further, the inherent losses from beam acceleration and transmission increases the probability that the higher mass beam currents will be at or below the minimum sensitivities of the monitoring devices. Currently we employ a series of 9 segment Faraday cups mounted on plunging arms to determine the position and intensity of the beams in the transfer line. Cup sensitivities are good for many ion species commonly used at the Bevatron but position resolution is poor and the method of detection is completely destructive. The process of tuning the beam down the transfer line is cumbersome and slow. A solution to this problem would be the development of a sensitive, partially destructive, wire grid system which is the subject of this paper.

### Design Philosophy

## Specifications and the Noise Environment

Using the current Faraday cup technology the machine operators can detect beam currents as low as 500 x  $10^{-9}$  amperes. Taking into account a 10% beam intercept, partial secondary electron multiplication, low noise electronics and improved electromagnetic (EMI) shielding we hope to construct a wire grid system with a factor of 50 to 500 times improvement in beam current sensitivity. This translates to a minimum detectible beam current of 1 to 10 x  $10^{-9}$  amperes. These levels would be particularly useful for the tuning and acceleration of the heavier ions.

Given these sensitivities the shielding against EMI and very large magnetic fields becomes quite critical. Several wire grid stations will be mounted on or near the main Bevatron quadrant magnets. Dynamic magnetic fields in this area may exceed intensities of 300 gauss per second or higher and contain many high frequency harmonics. At other wire grid locations the radio frequency (R.F.) noise from the Alvarez injector or the synchrotron R.F. system will have an adverse affect on any poorly shielded electronic system.

The profile monitors may also be used in a number of other locations in the Bevalac system. Beam pulse widths may vary in duration from 1 millisecond to greater than 1 second with periods ranging from 27 milliseconds to longer than several seconds. Since it has been specified that the operators need "real time" pulse to pulse information from one or more of the profile monitors the local data aquisition system must be able to process and deliver the information in a time shorter than the minimum pulse period of 27ms.

#### System Description

# Physical Layout

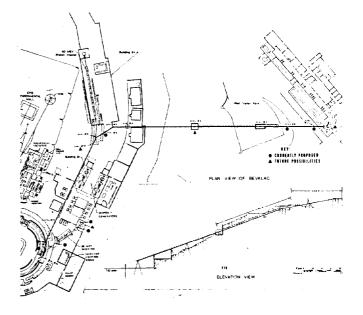

The initial system as seen in figure 1 consists of 12 profile grids and their associated data acquisition electronics. Starting at the output of the Heavy Ion Linear accelerator (SuperHILAC) they extend down the transfer line to the final station located inside the East Tangent Tank injection area. Four profile grids are also installed in the low and medium energy lines of the new local injector.[3] The information from each station is transmitted via a digital serial link to the main control computer located in the southern wing of the Bevatron building. Transmission line lengths to the more remote stations may exceed a quarter of a mile or more.

<sup>\*</sup>This work as supported by the Director, Office of Energy Research, Office of High Energy and Nuclear Physics, Nuclear Science Division, U. S. Department of Energy Under Contract Number DE-AC03-SF7600098.

# Electronic System

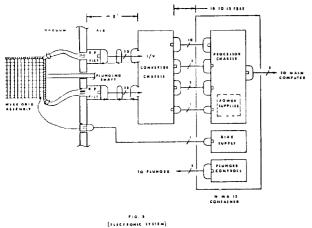

The basic electronic system (see Fig. 2) is composed of a wire grid array for sensing the beam, current to voltage converter electronics (I/V chassis), and a data acquisition system (processor chassis) which digitizes and transmits the profile data to the central computer which in turn converts the data to a visual record for the control room operators. Each system is described in further detail below.

### Fig. 2

## Wire Grid System

Each profile grid assembly consists of three 8.1 cm<sup>2</sup> parallel wire planes consisting of 32, .254 mm diameter wires. The outer grid planes generate the vertical and horizontal profiles while the central or bias grid serves a dual purpose as a collector of secondary electrons and an electrostatic shield. The physical arrangement of the grids is optimized for relative rather than absolute beam profile measurements. The grid wires are connected to the detector electronics via low noise coaxial cable chosen to reduce the 'turboelectric' effect [4] which has been observed at some stations mounted near vacuum pumping equipment. The cables pass through an in-house designed vacuum feedthrough and are terminated in an EMI-tight connector. The connector can optionally be fitted with miniature pi-network filters to block any extraneous rf energy that might be picked up in the vicinity of the injector. From the vacuum box connector the coaxial cables, which are surrounded by a second outer shield, are fed directly without interconnection into the the r.f. tight I/V chassis approximately .3 to 1.0 meters away.

## I/V Converter Electronics

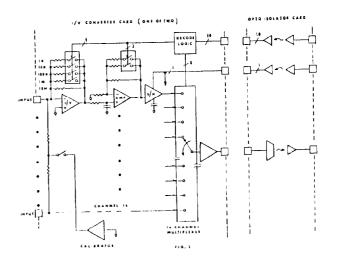

The I/V electronics are housed in a tightly shielded weatherized box which contains four moderately sized printed circuit (PC) boards mounted on a large unifying PC back plane. 64 coaxial cables from the wire grid assembly are terminated via a PC card edge connector onto a "cross connect board" which provides a user definable configuration of selected wire grid signals. Of these 64 signals a maximum of 32 may be selected for processing by two resident 16 channel I/V boards. A typical board, partially shown in Figure 2, consists of 16 identical channels of a gain selectable I/V amplifier, integrating filter, second stage amplifier, and a sample and hold (S/H) converter. The multiplexed outputs are transmitted serially through the fourth "optoisolator" board. Control the of I/V boards, which includes gain adjustment, S/H triggers and multiplexer timing also passes through the optoisolator board from the processor chassis (see Fig. 3).

The optoisolator board optically isolates all digital and analog signals from remote ground systems. This is done to suppress possible ground loop currents between the I/V and processor chassis that might be generated by ubiquitous dynamic fields in the vicinity of the Bevatron.

Optical isolation for the digital signals is provided by the HCPL-2601 [5] and for the analog signals by the BB3562 [6] optoisolation amplifier. As mentioned previously, beam pulse widths may be excessively long which necessarily requires that the amplifier channels be D.C. coupled. This fact implies that input amplifiers and following gain stages be specified for very low input bias currents and offset voltages over the anticipated temperature range. Further improvements in offset drifts beyond the performance of the electronics will be obtained by a D.C. restoration algorithm which resides in the processor chassis.

The selected input amplifier (OP-15) is a wide bandwidth, low noise (.01 pa/(hz)1/2), low bias current (60 pa) BIFET manufactured by Precision Monolithics. It is unconditionally stable and generates very low offset voltages even at the highest gain range and maximum operating temperature of 50 degrees centigrade. The wide bandwidth insures ideal current-to-voltage converter performance over the signal frequencies to be detected (f/3db = 5.0)khz). The output of the OP-15 is filtered and again amplified by a second very low offset (30 micro volts max) amplifier, the OP-07 [7]. Gain switching of both amplifiers is accomplished with low bias current FEI analog switches (DG-201) [8]. The sample and hold is a standard LF398 [9] and the multiplexer is a DG506A by Signetics. Included on each board is a current calibrator to test circuit operation.

Located from 1 to 5 meters away from the I/V chassis is a weatherized NIMA 12 panel enclosure which contains the processor chassis, power supplies, wire grid bias supply and plunger shaft controls. The power supplies and microprocessor were deliberately segregated from the sensitive I/V electronics to minimize any digital and A.C. line noise.

The processor, one of five 11.43 cm by 15.24 cm cards, employs an Intel 8085 microprocessor I.C. with 2k of RAM and 4k of ROM memory. On the same board resides an 8255 I/O chip and a 12 bit A/D (AD574) manufactured by Analog Devices. Analog levels from the I/V chassis are digitized and stored in the processor memory for later transmission. The instruction speed of the 8085 is quite adequate to perform the required software tasks to process and transmit all the necessary data between pulses.

The software requirements are fairly straight-forward. The sampled beam pulse must be digitized and stored in the local memory and then transmitted to main computer. The control program along with the communications protocol is stored in RDM memory. In addition there are several algorithms that enhance the operation of I/V converter electronics.

The first, mentioned previously, is a D.C. restoration program designed to remove any residual D.C. offsets in the converter electronics. This is accomplished by sampling the wire grids between beam pulses and summing that data with the beam profile records. The second feature is an automatic gain control (AGC) routine designed to compute a running average of the beam current profile and automatically adjust the amplifier gains accordingly. If desired this routine can be changed to manual control by the machine operators.

The remaining four cards provide a high speed serial (1.0 Mhz) communications interface between each processor and the main control computer. Data transmission is accomplished by pulse width modulation (PDM) techniques.

## Central Computer

The data record generated by each of the profile monitors will be updated every pulse. Specific records from selected stations chosen by the operators will transmit their data to the Bevatron central computer (Mod. Comp. 4/35 [10]) between pulses. Specifically the data base and graphics generating routines will reside in a subsystem computer (Mod. Comp. 2 [10]) which will deliver a video display by command to the Mod. Comp. 4.

#### Project Status

To the date of this article a prototype version of wire grid chamber and I/V chassis are near completion and are to be tested in the transfer line in the month of June. Tests will include functionality, sensitivity, and immunity to EMI. Construction of the prototype processor chassis will begin in May along with the software development for the microprocessors and the main computer.

## References

[1] A. Ghiorso et al, "The Bevalac - An Economical Facility for Very Energetic Heavy Particle Research", 1973 PAC, NS-20, No. 3, San Francisco, 1973, p. 155.

- [2] R.T. Avery et al, "Performance of the New Cryogenic Vacuum System at the Bevatron," 1983 PAC, NS-30, No 4, Santa Fe, 1983, p.2895.

- [3] J. Staples, et al, "Heavy Ion Upgrade of the Bevatron Local Injector", 1984 Linear Accel. Conf., Seeheim/Darmstadt, West Germany.

- [4] Keithly Instr. Inc., "Low Level Measurements", p 24, 3rd ed., copyright 1984, Keithly Instr., 3rd ed.

- [5] Device and numeric designation by Hewlett Packard.

- [6] Device and numeric designation by Burr Brown Inc.

- [7] Device and numeric designation by Precision Monolithics.

- [8] Device and numeric designation by Siliconix Inc.

- [9] Device and numeric designation by National Semiconductor.

- [10] Device and numeric designation by Modular Computing Inc.